引言

买芯片网专注整合全球优质莱迪思代理商现货资源,是国内领先的Altera(英特尔)、Lattice(莱迪思)、Xilinx(赛灵思 AMD)芯片采购服务平台,买芯片网轻松满足您的芯片采购需求.

通过按钮与消费电子产品进行互动的时代已经过去。人机交互在过去几年中发生了巨大变化并仍不断发展。本文将提供人机界面变化的一些实例,帮助读者更充分地了解如何使用一种特别的架构实现低功耗解决方案,提升电池供电应用的用户体验。该架构由基于低功耗FPGA实现的异构处理单元实现。

人机界面(HMI)发展趋势

大多数移动设备在被唤醒进入工作之前都会进入睡眠或低功耗模式,所以您与设备的第一次交互操作即是唤醒。这种“唤醒”可以通过手腕翻转、摇动、单击或双击、来电或消息、机械按钮按压以及特定短语、手势或声音(例如拍手或打响指)触发。每种“唤醒”方法都需要使用传感器和监测装置来侦测特定的动作。“唤醒”操作必须以极低的功耗实现。现在的低功耗FPGA能够以大约100uW的功耗实现实时在线、实时聆听解决方案,而未来功耗还能显著降低。

实现创新的HMI解决方案所需的各种传感器正在迅速改变I/O发展的格局。现在的移动设备需要更高的I/O速率。在过去几年中,低成本传感器的激增以及全新的更高性能接口的广泛采用增加了这类系统的计算需求。而对实时在线功能的需求也在不断增长传感器在无人机、电话、可穿戴设备和工业设备等各种应用中持续收集大量数据。系统设计工程师需要在加快数据处理的同时降低系统功耗,在不再次充电的情况下满足消费者一整天的设备使用需求。

移动系统设计需要一种更全面并基于系统的解决方案,而不是以CPU为中心的传统设计方法。系统设计工程师需要充分利用处理器的差异性来尽可能降低功耗,与此同时满足当今移动设备日益增长的计算需求。

欢迎来到分布式异构处理(DistributedHeterogeneousProcessing,DHP)的时代

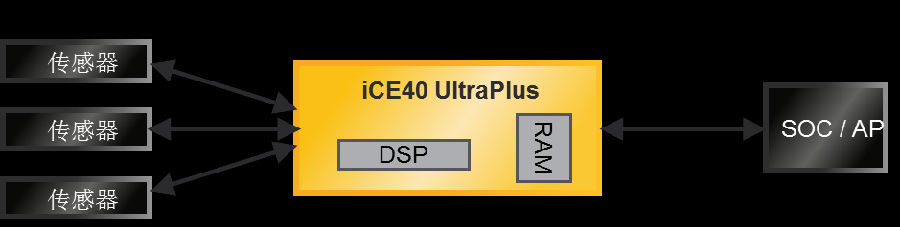

DHP是一种全新的低功耗解决方案,使用本地算法而不是云端算法,使用不同的处理器而不是功耗很高的应用处理器(AP)。通过这种设计,设计工程师可以使用并行处理技术满足复杂协处理的新需求,使用本地数字信号处理器(DSP)执行重复的数据处理任务,降低功耗并使应用处理器不再参与某些处理任务,从而使其能够长时间地处于睡眠模式以节省系统功耗和延长电池使用时间。

分布式异构处理本地处理可降低功耗并加速响应

更多存储空间、更多DSP

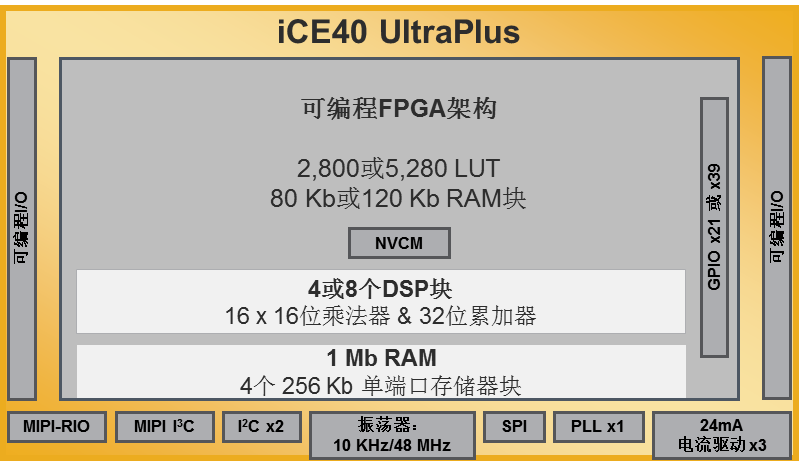

莱迪思半导体公司为iCE40UltraFPGA产品系列添加了新成员,可满足对于DHP计算需求,帮助设计工程师实现功耗更低的解决方案,相比上一代产品具备8倍的存储空间和2倍的DSP。全新的iCE40UltraPlusFPGA拥有更多逻辑资源,静态电流仍仅需75μA,而上代产品的静态电流为71μA。

iCE40UltraPlusFPGA提供多种封装尺寸,使得设计工程师能够为当今竞争激烈的移动市场快速构建独一无二并且极具吸引力的解决方案,满足下一代消费电子、移动、物联网边缘和工业产品的严苛处理需求。

该全新的FPGA属于低功耗iCE40产品线。iCE40Ultra系列结合了低功耗和高度集成的功能等特性,包括多个16x16位乘法器块以及超小的封装尺寸。

全新iCE40UltraPlusFPGA为用于重复数字处理的低功耗并行处理解决方案提供所需的全部关键资源。1.1Mbit低功耗SP-SRAM、8个乘法器/累加器块用于信号处理,高达5280LUT用于用户逻辑,以及用于瞬时启动应用的非易失性配置存储器,iCE40UltraPlus解决方案为设计工程师实现实时传感器缓存、声束形成音频子系统和其他重复计算密集型应用提供了理想的蓝图。该器件也可以用于支持各种桥接、缓存和显示应用,助力加速下一代移动和工业应用的创新。

莱迪思iCE40UltraPlusFPGA框图

全新的iCE40UltraPlusFPGA还添加了可提供设计灵活性的可编程I/O、支持始终在线摄像头应用的I3C接口(由MIPI定义的全新高带宽数据和控制传感器接口)以及内置振荡器,能够降低功耗和BOM成本。

功能丰富的iCE40UltraPlusFPGA静态功耗低至75μA,封装尺寸小至2.15x2.55mm,适用于要求功耗极小、空间受限的消费电子类应用。该器件还提供QFN封装,支持工业和其他消费电子类应用使用的低成本PCB组装。

为了加速产品开发,莱迪思半导体公司提供iCE40UltraPlusFPGA系列的整套工具以及评估样片和开发板。莱迪思iCE40UltraPlusFPGA能够加速产品上市进程的另一个因素是认识到了嵌入式系统开发工程师所具备的特殊经验技能。尽管FPGA历史悠久并且也得到了广泛的采用,但相比MCU而言仍是设计工程师们不太熟悉的产品。这一点都不奇怪,现在懂得MCU编程的工程师要比懂得FPGA编程的多得多。开发工程师现在可以通过在iCE40UltraPlusFPGA中实现软核处理器来解决这个问题。事实上,大容量SPRAM和固化的DSP块使iCE40UltraPlusFPGA成为实现软核处理器的理想平台。为了支持这些解决方案,RISC-V组织(www.riscv.org)发布了一个开源、可扩展、高效的处理器设计。在最近的RISC-V研讨会上,有两家公司使用RISC-V开源软件工具和LatticeFPGA工具实现了基于莱迪思iCE40UltraPlusFPGA的RISC-V软核。这两家的公司的行动证明iCE40UltraPlusFPGA可用于开发高度集成并行加速器的专用软处理器,并且开发成本非常低。这为具备MCU技能的工程师提供了前所未有的灵活性。

潜在应用

iCE40UltraPlusFPGA具备的嵌入式DSP支持设计工程师运行更高质量的算法,而1Mbit片上SRAM则允许系统在较低功耗的状态下缓存数据。在越来越多的系统中,设计工程师需要一个器件作为应用处理器的协处理器,并且可以在系统关闭时处理和分析数据,然后唤醒应用处理器以执行更复杂的功能。

潜在的应用几乎是无限的。例如,可穿戴或白色家电市场中的许多解决方案都需要用于大容量帧缓存和接口桥接的器件。iCE40UltraPlusFPGA凭借其大容量片上SRAM可支持实时工作显示屏,而此时应用处理器仍能处于睡眠模式。同时,iCE40UltraPlusFPGA还可以实现MCU和显示器之间的桥接。该FPGA支持MIPIDSI或并行接口,为自定义图形加速以及I/O扩展提供灵活性。显示驱动器和图形引擎的结合可媲美低成本GPU,而功耗却大大降低。

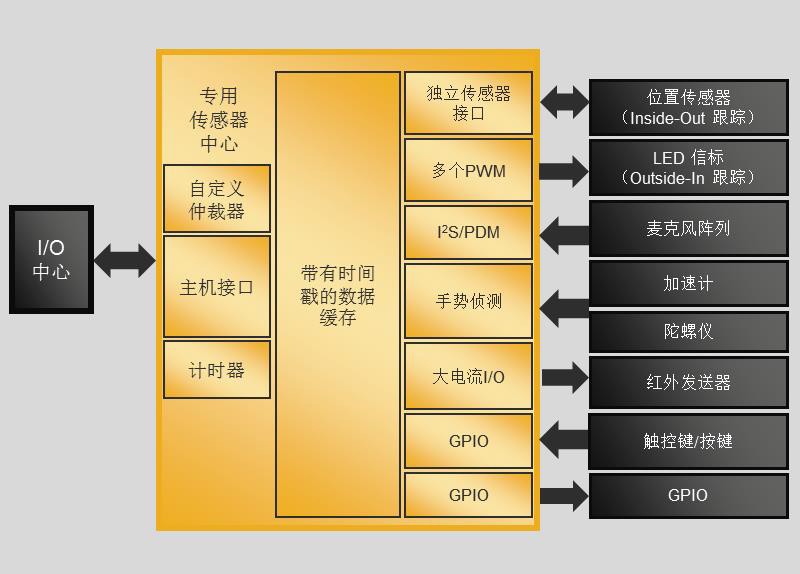

在第二类应用中,许多电池供电的设备需要实时传感器缓存,以便在应用处理器处于睡眠模式时执行传感和检测加速。这些器件必须屏蔽假唤醒,使得应用处理器更长时间地处于睡眠模式。在这类应用中,iCE40UltraPlusFPGA可应用于各种传感器和应用处理器之间以处理唤醒触发,如用于计步器上的双击或“摇一摇唤醒”技术。类似的应用还有动作检测以及指纹、手势或虹膜扫描等。

实时传感器缓存

这些功能都需要两步过程。首先,系统必须确定是否发生了适当的唤醒动作。其次,系统必须确定所使用的手势或指纹是否正确以获得对系统的访问。对于以前的应用而言,如果发生了适当的动作,FPGA就会唤醒应用处理器。而iCE40UltraPlusFPGA凭借其大容量片上存储空间,现在可以在系统唤醒之前执行上述两个步骤,从而使得应用处理器更长时间地处于睡眠模式。

iCE40UltraPlusFPGA的第三类潜在应用是声束形成。现在的系统常常需要增强的音频处理功能,将特定的音频信号与高噪声环境分离。一个典型应用就是系统必须在多人正在说话的房间中检测并接受来自一个人的语音命令。

使用多个麦克风阵列和波束成形技术可检测特定的声音并滤除不需要的噪声。亚马逊最近推出的Echo平台是一个很好的例子。这种免提音箱使用波束成形技术和7个麦克风,可以从室内环境中辨别出用户的声音,即使室内正播放着音乐也没问题。

然而,大多数应用处理器仅支持两个麦克风。而且这些系统通常必须始终开启并且使用电池供电,对于大功耗的应用处理器而言是难以完成的任务。那么设计工程师该如何实现24小时不间断并以最低功耗支持多达七个不同麦克风输入的波束成形解决方案呢?

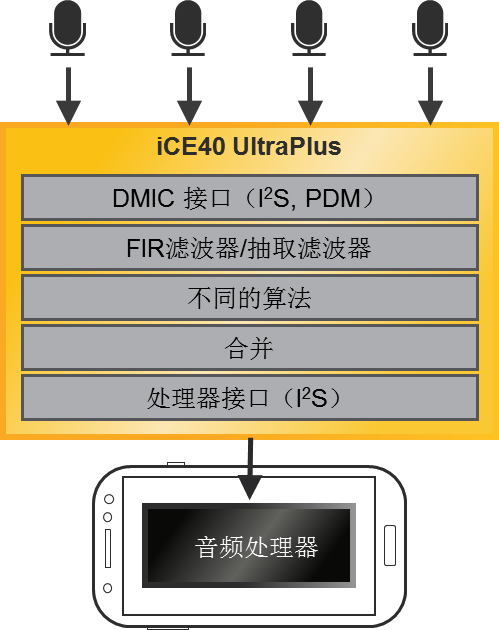

一种方法是将麦克风阵列连接到一片低功耗的iCE40UltraPlusFPGA。

麦克风阵列声束形成

上述解决方案支持多个数字麦克风PDM输入。片上乘法器和累加器(MAC)块可用于PDM抽取和滤波,FPGA的大容量存储空间则可支持麦克风延迟线。这种方案也为系统设计工程师提供了更多创新空间。他们可以使用片上MAC和FPGA构建高度灵活的波束形成滤波器或噪声消除系统以及音频均衡功能。

iCE40UltraPlusFPGA可通过各种工业接口(如I2S、soundwire、SlimBu等)连接到音频处理器。与任何基于FPGA的解决方案一样,设计工程师可以使用片上嵌入式DSP、逻辑和存储器资源构建高度定制解决方案并快速推向市场。

信号聚合

莱迪思iCE40UltraPlusFPGA提供的资源也可用于大大简化移动设备中的印刷电路板(PCB)布局。低成本传感器的快速增长以及实时在线监测和环境感知计算的出现给PCB设计工程师带来了新的挑战。移动设备中的每种新型传感器必须与应用处理器进行通信。

这些系统经常使用I2C、I3C、SPI、UART和MIPIDPHYCSI-2等接口。设计工程师可能要在单个产品中管理多达40个传感器到应用处理器的信号。

通常情况下,围绕着移动设备电池的一般有两块PCB。这些PCB通常使用提供有限EMI屏蔽的柔性线缆连接。柔性线缆被限制为两层以尽可能降低成本。因此电路板布局工程师可能需要应对在具有信号振铃和其他可靠性问题的双层线缆上传输多达40个信号的挑战。

利用莱迪思iCE40UltraPlusFPGA的独家特性来聚合这些系统中的许多信号是一种简化上述工作的方法。将iCE40UltraPlusFPGA放在传感器旁,PCB设计工程师可以使用简单的单针或双针接口将多个不同的信号聚合并传输到应用处理器。

莱迪思iCE40FPGA为信号聚合和快速布局调整提供了灵活的I/O中心

实现信号聚合带来的好处并不仅限于此。如上文所述,莱迪思iCE40UltraPlusFPGA可提供大量的计算资源。片上查找表(LookUpTable,LUT)和DSP可用于执行更多的本地化DHP任务。例如,声束形成系统必须唤醒应用处理器以检测和验证指令中的关键短语。而使用信号聚合时,设计工程师可以利用iCE40UltraPlusFPGA的本地资源在唤醒应用理器之前检测和验证关键短语。这种方法不仅为用户提供了对关键短语的更快响应,它还通过使应用处理器在睡眠模式中保持更长时间而降低了系统功耗。

信号聚合大大简化了应用处理器PCB板的布局。通过最小化板上信号的数量,设计工程师可以更容易地满足复杂的布局规则并更快地完成电路板布局。

最后,使用iCE40UltraPlusFPGA实现信号聚合可带来巨大的设计灵活性。设计工程师可以重新配置iCE40UltraPlusFPGA上任何接口的位置以简化电路板布局。在这种情况下,是理想的电路板布局决定FPGA引脚排列,而不是反向为之。

总结

I/O接口的快速发展有望为移动系统设计带来令人兴奋的全新功能。低成本传感器的激增和“实时在线”功能的广泛采用将使设计工程师实现前所未有的个性化设计。但要实现这些新功能,设计工程师必须为移动设备采用异构处理解决方案,使用不同的处理模块来延长电池使用时间。凭借DSP块和片上存储器,莱迪思半导体的iCE40UltraPlusFPGA可帮助OEM厂商将这些引人注目的新功能添加到产品中,满足下一代移动设备颇具挑战性功耗和计算要求。